# A Divider-less Automatic Frequency Calibration for Millimeter-Wave Sub-Sampling Phase-Locked Loops

P. Kurth, U. Hecht, E. Wittenhagen and F. Gerfers

Mixed Signal Circuit Design, Technische Universität Berlin, Einsteinufer 17, 10587 Berlin, Germany https://orcid.org/0000-0002-6164-5756

*Abstract*—This paper presents a novel divider-less scheme for automatic frequency calibration (AFC) of sub-sampling phaselocked loops. The proposed system works without any frequency dividers at all by utilizing the phase information provided by serialized frequency detection through a sub-sampling phase detector. The detector is driven by evenly-spaced reference signals, which enables frequency detection and correction. The AFC is accompanied by a novel divider-less lock detector, which is also sample-based. The proposed system is configured to detect and correct all possible lock frequencies within the oscillator tuning range and is built, apart from the analog front-end, only with synthesizable standard cell CMOS logic.

Index Terms-SSPLL, AFC, Divider-less, Lock Detector

## I. INTRODUCTION

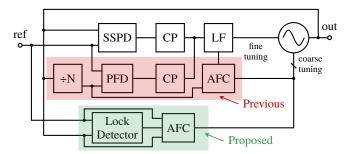

Sub-sampling phase-locked loops (SSPLL) enable PLLs with ultra-low-jitter [1] due to their inherent feature of not multiplying the loop noise by  $N^2$  (N = ratio between input and output frequency) [2]. This works by exploiting signal aliasing of the output signal by using a track-and-hold circuit (T&H) with the reference signal as clock. While this produces excellent phase noise results, the sub-sampling phase detector (SSPD) can not distinguish between any integer multiples of the reference frequency, hence the PLL can "false lock" to an undesired frequency. To solve this issue, typically a secondary modified type-II charge pump PLL as shown in Fig. 1 is employed [1]–[3], which only detects frequency and helps the core PLL lock to the correct frequency. As this secondary PLL uses a modified phase-frequency detector (PFD) clocked with the reference frequency, the oscillator signal needs to be divided down to the reference frequency. At millimeter-wave (mmw) frequencies, these dividers (e.g. injection-locked, current-modelogic) are a challenge to design and have high power and area consumption [4]. In theory, the frequency-detection path could be disabled after a true lock, but this is an unreliable solution due to possible lock loss with varying temperature or voltage variations. Furthermore, high-frequency dividers are analog circuits, often relying on bandwidth enhancements through inductors, which do not scale well with technology.

To circumvent these challenges, we propose a novel dividerless frequency-acquisition scheme for SSPLLs which is based on sequential logic and therefore easy to develop and synthesizable. This enables SSPLLs to be built entirely without frequency dividers and secondary PLLs. Furthermore, the proposed system scales well with technology advancements. The used SSPLL is designed for an output frequency of 56 GHz with a reference

Fig. 1: System architecture of an SSPLL with a secondary charge-pump PLL (red) for frequency acquisition and the proposed AFC (green)

frequency of 875 MHz. This serves as demonstration of the novel AFC, but the principle can be employed for any SSPLL.

This paper is organized as follows: First the general principle of the frequency-acquisition scheme is described in section II. Following that, in section III the actual implementation is discussed alongside with practical improvements and simplifications. The simulation results are shown in section IV, the proposed work is concluded in section V.

#### II. PRINCIPLE

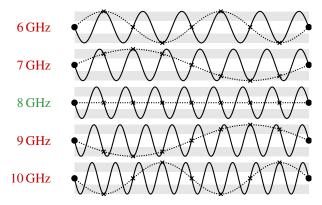

Once a SSPLL is in lock, the SSPD samples the oscillator signal at exactly the zero crossings. In this state, the output signal of the oscillator looks like a constant voltage after the phase detector. If more than one sampler is used with equidistant sampling points, the voltage after all samplers will not be necessarily constant. This depends on the specific ratio between the input and the output frequency. Using more than one sampler can be seen as increasing the effective Nyquist frequency  $f_{\rm ref, eff}$ , although the reference frequency stays the same. If the output frequency is an integer multiple of  $f_{\text{ref.eff}}$ , the SSPLL is in true lock. Otherwise, some of the samples will not lie at the zero crossings, producing characteristic patterns, depending on the lock frequency. Fig. 2 shows an example for a PLL with N = 8 with a true lock (8 GHz) and several false locks. The reference frequency is 1 GHz, 7 auxiliary samplers are used. This leads to an effective sampling frequency of 8 GHz. In the case of the true lock, all sampling points occur at the zero crossings, while in false lock the output frequency is aliased to some non-zero frequency.

This property can be used to find the state the PLL has locked in. In lock (true or false), the output frequency of

This paper has been accepted for publication as: P. Kurth, U. Hecht, E. Wittenhagen and F. Gerfers, "A Divider-less Automatic Frequency Calibration for Millimeter-Wave Sub-Sampling Phase-Locked Loops", 2021 IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Lansing, MI, USA, 2021, pp. 718-721, doi: 10.1109/MWSCAS47672.2021.9531889.

<sup>© 2021</sup> IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Fig. 2: Sampling of the oscillator signal at equidistant time points for different possible PLL lock frequencies (locking to the falling edge). The dots represent the main SSPD sampling points, the crosses are the samples of the auxiliary samplers. The shaded areas mark the different windows of the comparator.

the PLL will always be an integer multiple of the reference frequency. Therefore, the number of auxiliary samplers  $N_{aux}$ must be chosen in order to create non-DC signals for all possible integer multiples of the reference frequency within the frequency range of the oscillator. Additionally, the pattern captured by the auxiliary samplers in true lock should be unique to distinguish true from false lock. The simplest solution is to make sure that the effective reference frequency  $f_{ref,eff}$  is an integer divisor of the oscillator output frequency. With these two constraints for the minimum number of auxiliary samplers can be calculated: In false lock, the time distance between the sample points must not fit any integer multiple of half of the period of the oscillator signal and in true lock all samplers must sample the same constant voltage:

$$\frac{1}{f_{\text{ref}} \cdot (N_{\text{aux}} + 1)} \begin{cases} \neq k \cdot 1/(2 \cdot f_{\text{lock}}) \\ = k \cdot 1/(2 \cdot N \cdot f_{\text{ref}}) \end{cases}$$

(1)

Here, k is a positive integer,  $f_{lock}$  is any frequency the PLL can lock to, which means only integer multiples of  $f_{ref}$  within the oscillator frequency range. With the oscillator center frequency  $f_0$  and the maximum (one-sided) tuning range  $\Delta f$  the PLL output frequency in lock can be expressed as:

$$f_{\text{lock}} = (N \pm i) \cdot f_{\text{ref}} \quad \text{with } i \in \left\{1, \dots, \left\lceil \frac{\Delta f}{f_{\text{ref}}} \right\rceil\right\}$$

(2)

This allows to rewrite (1) as:

$$\frac{2(N \pm i)}{N_{\text{aux}} + 1} \begin{cases} \neq k & \text{for } i \neq 0 \\ = k & \text{for } i = 0 \end{cases}$$

(3)

This criterion has to be checked against every possible i (see (2)), which is best done numerically. Table I shows some examples of the required number of auxiliary samplers for different PLL frequency rations and oscillator tuning ranges. The number of required sampler increases with the tuning range of the oscillator, as more possible locking frequencies exist. This still is feasible for low ratios between the input and output frequency, but for high ratios with high tuning ranges more

TABLE I: Required number of auxiliary samplers depending on the PLL factor  $N (f_{out}/f_{ref})$  and the oscillator tuning range

| $\Delta f/f_0$ | N = 8 | N = 64 | N = 1000 |

|----------------|-------|--------|----------|

| 5 %            | 3     | 15     | 124      |

| 10 %           | 3     | 15     | 124      |

| 25 %           | 7     | 63     | 999      |

| 50 %           | 15    | 127    | 1999     |

samplers than what is reasonable to implement are needed. This problem is addressed in section III.

With the frequency information provided by the auxiliary samplers, the frequency state can be decoded. For this, the samplers are followed by window comparators which detect whether a sample is high, low or zero. For each locked frequency there is a specific and unique pattern, so the exact frequency can be derived. In Fig. 2 the comparator regions are annotated and the patterns can be seen, e.g. for 7 GHz there are three high values, one zero value and three low values. The frequency state can be directly assigned by a look-up table.

# III. IMPLEMENTATION

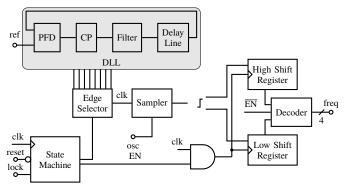

In this section, the implementation of the proposed AFC is presented and the differences to the general operation principle will be highlighted. The system is shown in Fig. 3. The SSPLL is designed for a reference frequency of 875 MHz and an output frequency of 56 GHz (N = 64). The tuning range of the LC-VCO is roughly  $\pm 6$  GHz, which requires 15 auxiliary samplers. The proposed AFC was implemented in a 22 nm fully-depleted silicon-on-insulator technology (FDSOI).

# A. Sampler Array

The proposed AFC needs an array of Naux auxiliary samplers additionally to the main sampler in the SSPD. For mmw-SSPLLs the sampling capacitance poses a serious load on the oscillator, requiring additional area- and power-consuming buffers. Especially for VCOs with wide variation ranges, a high number of auxiliary samplers are needed. Therefore, this implementation does not actually use  $N_{aux}$  physical samplers, but only one, which is controlled by a delayed reference signal with a varying delay time. This continuously shifts the sampling time point. Therefore, the entire process of the detection of the PLL frequency state is serialized, which also helps on the comparator requirements, as only one is needed. The AFC uses a shift register to store the individual comparator outputs for each sample. The serialized approach takes a longer time than a parallel detection, but this is negligible, as this is not a time-critical process. The sampling capacitance of the auxiliary sampler is kept small (5 fF), as low noise is not of importance in this case. In order to reject charge injection errors and voltage variations in the hold phase, fully-differential samplers with cross-coupling are used.

### B. Comparator

The comparator follows the sampler and needs to decide whether the sampled value is high, low or zero. Therefore, a window comparator is needed. The implemented comparator

This paper has been accepted for publication as: P. Kurth, U. Hecht, E. Wittenhagen and F. Gerfers, "A Divider-less Automatic Frequency Calibration for Millimeter-Wave Sub-Sampling Phase-Locked Loops", 2021 IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Lansing, MI, USA, 2021, pp. 718-721, doi: 10.1109/MWSCAS47672.2021.9531889.

<sup>© 2021</sup> IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

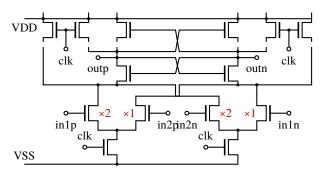

Fig. 3: AFC implementation

uses two fully-differential strongARM latches [5], shown in Fig. 4, for the high/low decision. The symmetric design cancels voltage droop and clock feed-through, which are quite high due to the small sampling capacitance. For greater noise margin and timing errors of the samples especially at the signal zero crossings (where the voltage change is the fastest), a deliberate offset of around 150 mV is introduced by sizing the input transistors differently (see Fig. 4). After each decision, the data is stored in two shift registers (one for each bit high/low).

# C. Clock Delay and Edge Selector

The proposed AFC needs  $N_{aux}$  delayed clock signals (regardless whether the detection is serialized or not), which are provided by a delay-locked loop (DLL). The resolution of the DLL must be at least  $T_{ref}/(N_{aux}+1)$ . As the sampling process is serialized, a clock edge selector is needed to choose the next sampling phase. The selector cycles backwards through all clock phases, as this prevents glitches during the update of the selection signal. The inherit reordering of the samples can can simply be fixed in the decoder.

The DLL is implemented following standard design practice, comprising a PFD as well as a charge pump and a delay chain with 32 current-starved inverters delays.

## D. Decoder

The decoder maps the digital output of the comparators/shift registers to a frequency state and controls the coarse tuning setting of the oscillator. In this implementation, the oscillator features a four-bit tuning word. The decoder is realized as a look-up table, where every possible state is represented. The corresponding states can be calculated from the specifics of the given PLL architecture (its output frequency, frequency range, reference frequency etc.). For example, in Fig. 2 at 7 GHz, there are three high (H), one zero (0) and three low (L) values (HHHOLLL), whereas for 10 GHz it is LOHOLOH.

In SSPLLs, the polarity of the gain of the charge pump can be negative or positive. This does not break the negative feedback, but changes whether the PLL locks to the rising or the falling edge. This also affects the detection of the state in the AFC. Fig. 2 showns a falling-edge type, for a rising edge type the values are simply mirrored around the true lock, for example 0L0H0L0H0 becomes 0H0L0H0L0.

Fig. 4: Implementation of the comparator with offset. The AFC uses only one input branch (left/right) for the samples.

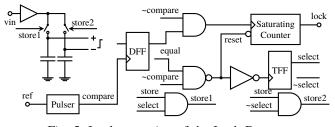

Fig. 5: Implementation of the Lock Detector

## E. Lock Detector

Contrary to a frequency correction with a PFD, where the secondary loop can run continuously, the proposed AFC must only operate while the SSPLL is locked (false or true lock). Therefore the implementation of the AFC needs a lock detector. Conventionally, a lock detector is built with digital gates [6], which cannot be operated at mmw-frequencies, therefore these lock detectors operate in the frequency-divided path. In the proposed implementation, the sampled voltage (after the SSPD) is monitored. If the SSPLL is in lock, it is constant and the proposed lock detector checks if enough consecutive samples are equal by comparing the previous and current sample by reusing the window comparator. If the values are equal, a counter is incremented. When the counter reaches a certain threshold, the SSPLL is assumed to be in lock. If on the other hand the values are different, the counter is reset and the previous value is updated by simply swapping the status of the storage location (previous  $\leftrightarrow$  current). The implementation of the lock detector is shown in Fig. 5.

An example of the lock detector waveforms is given in Fig. 6. In regions with slow voltage changes the counter starts accumulating, as there are a few consecutive values that are considered equal. However, only after the PLL is locked the counter accumulates until the lock detection flag is set. For the visualization, the final value of the counter is set to a low value, in the real implementation this value is set higher.

#### **IV. SIMULATION RESULTS**

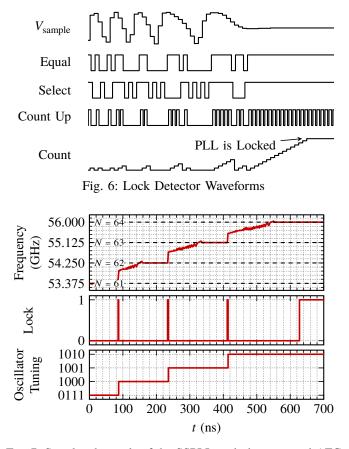

Figure 7 shows the simulated waveforms of the proposed AFC. The first graph shows the voltage after the track-and-hold in the hold phase. The second graph shows the output frequency of the PLL. There are four events where the PLL is locked (at

This paper has been accepted for publication as: P. Kurth, U. Hecht, E. Wittenhagen and F. Gerfers, "A Divider-less Automatic Frequency Calibration for Millimeter-Wave Sub-Sampling Phase-Locked Loops", 2021 IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Lansing, MI, USA, 2021, pp. 718-721, doi: 10.1109/MWSCAS47672.2021.9531889.

<sup>© 2021</sup> IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Fig. 7: Simulated signals of the SSPLL with the proposed AFC

85 ns, 235 ns, 420 ns and 630 ns). This can be seen in the output frequency and the lock detector/AFC signals. However, the first three locks are false locks. At each of these events, the lock detector correctly detects the lock, triggering the AFC. For the three false lock cases, the the digital coarse frequency setting is updated correspondingly (in these scenarios the setting is increased). As the PLL quickly loses lock, the lock detection signal is reset again. The fourth case shows then the true lock, where the lock detection signal stays set and the coarse tuning remains unchanged. The output frequency is now correct at 56 GHz and the PLL is in true lock.

# V. CONCLUSION

This paper demonstrates the design of a divider-less circuit for automatic frequency calibration of sub-sampling phaselocked loops. Apart from the analog samplers, DLL and comparators, the system is entirely digital and synthesizable. Furthermore, only the samplers operate at the PLL output frequency, the remaining circuits are implemented for the lower reference frequency. As the system is mainly digital with small analog circuits, the area consumption can be very low, especially compared to huge inductor-based frequency dividers (bandwidth-enhanced CML or injection-locked). The proposed principle is easy to adapt to different PLL configurations (oscillator tuning range, input/output frequency ratio) and is independent of oscillator/charge pump/filter architecture (e.g.

| Work                                     | [1]             | [7]                | [8]              | This work                 |

|------------------------------------------|-----------------|--------------------|------------------|---------------------------|

| Technology<br>(nm)                       | 40              | 180                | 65               | 22 (FDSOI)                |

| Frequency<br>(GHz)                       | 14              | 2.3                | 40.5             | 56                        |

| Reference<br>Frequency (GHz)             | 200             | 48                 | 100              | 875                       |

| Methodology                              | FLL             | FLL<br>+ Counter   | Secondary<br>PLL | Sub-sampling<br>with DLL  |

| FLL/AFC<br>DC Power (mW)                 | 1.5             | 46.7 <sup>\$</sup> | 4.59             | 1.1                       |

| Divider<br>AFC/FLL Area (µm <sup>2</sup> | ÷ 70<br>) 8600* | ÷ 2<br>35 600*     | none<br>33 600*  | none<br>2000 <sup>#</sup> |

| in chi EE mea (µm                        | , 0000          | 55 500             | 55 500           | 2000                      |

<sup>\$</sup> Total PLL power consumption

\* Estimated from die photograph <sup>#</sup> Pre-layout estimation

TABLE II: Comparison with state-of-the-art

it is also applicable in digital SSPLLs). Additionally, the system can operate continuously while maintaining a low power consumption by periodically running a frequency test.

Table II shows the comparison with the state of the art. In [7], a counter-based AFC is used, but this requires divideby-two quadrature dividers and the PLL operates at much lower frequencies (2.3 GHz). In [8] a truly divider-less SSPLL design is presented which employs a secondary PLL for highfrequency reference generation and uses a similar principle as shown in this work. However, a significantly increased reference frequency is used, which is often not feasible, especially for twostage PLLs. Compared to similar designs, this work provides an AFC scheme optimally suited for mmw-SSPLLs.

#### ACKNOWLEDGMENT

The authors would like to thank GLOBALFOUNDRIES for the University Multi Project Wafer Program and the BMBF (German Ministry for Education and Research) for funding this work within the *fast* initiative. Furthermore, the authors would like to thank Ravi Subramanian and Mentor for Analog FastSPICE (AFS) support.

#### References

- Z. Zhang *et al.*, "A 0.65-V 12–16-GHz Sub-Sampling PLL With 56.4fsrms Integrated Jitter and –256.4-dB FoM," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 6, pp. 1665–1683, 2020.

- [2] Xiang Gao et al., "Sub-Sampling PLL Techniques," in 2015 IEEE Custom Integrated Circuits Conference (CICC), Sep. 2015, pp. 1–8.

- [3] K. Raczkowski et al., "A 9.2–12.7 GHz Wideband Fractional-N Subsampling PLL in 28 nm CMOS With 280 fs RMS Jitter," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 5, pp. 1203–1213, 2015.

- [4] T. Siriburanon et al., "A 60-GHz Sub-Sampling Frequency Synthesizer Using Sub-Harmonic Injection-Locked Quadrature Oscillators," in 2014 IEEE Radio Frequency Integrated Circuits Symposium, 2014, pp. 105– 108.

- [5] B. Razavi, "The StrongARM Latch [A Circuit for All Seasons]," IEEE Solid-State Circuits Magazine, vol. 7, no. 2, pp. 12–17, 2015.

- [6] C. Chen *et al.*, "A Fast-locking Clock and Data Recovery Circuit with A Lock Detector Loop," in 2011 International Symposium on Integrated Circuits, 2011, pp. 332–335.

- [7] W. Chang et al., "A Fractional-N Divider-Less Phase-Locked Loop With a Subsampling Phase Detector," *IEEE Journal of Solid-State Circuits*, vol. 49, no. 12, pp. 2964–2975, 2014.

- [8] Wang, Hao *et al.*, "Low-Power and Low-Noise Millimeter-Wave SSPLL With Subsampling Lock Detector for Automatic Dividerless Frequency Acquisition," *IEEE Transactions on Microwave Theory and Techniques*, vol. 69, no. 1, pp. 469–481, 2021.

This paper has been accepted for publication as: P. Kurth, U. Hecht, E. Wittenhagen and F. Gerfers, "A Divider-less Automatic Frequency Calibration for Millimeter-Wave Sub-Sampling Phase-Locked Loops", 2021 IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Lansing, MI, USA, 2021, pp. 718-721, doi: 10.1109/MWSCAS47672.2021.9531889.

<sup>© 2021</sup> IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.